Homework 4B

What’s due

- HDL: As with prior assignments, your completed HDL needs to be submitted (via GitHub) to Gradescope. A significant portion of the grade comes from passing unit tests.

- Questions: The GitHub submission needs to include completed answer to the questions in

questions.mdin the repo. - Demo: An in-person demo is required for part of the grade. The demo needs to be completed during office hours within 10 days after the assignment is officially due. Demos can not be done until after spring break, but must be completed by March 28th. Late penalties are based on the Gradescope submission, not the completion of the demo.

Setup

Create a repo via this link

The Wonder Washer: Reloaded

SH Enterprises loved your work on the Wonder Washer design and would like to manufacture some prototypes! They’ve decided to utilize programmable logic (using FPGAs) for the first few test machines, which will allow them to adjust the machine as needed. They’d like you to redesign your work using SystemVerilog and to incorporate some minor changes.

(Re)Design

- The original port names, types, and sizes will still be used. You also need to match the behavior from your prior work. Refer to Homework 3B for details.

- Three new ports will be added:

-

Idleis an output that will indicate when the machine is idle (not washing anything and waiting for the start) -

Resetis an asynchronous reset (input), that resets the state machine to the idle state. -

Enableis an input that enables state changes. That is, the machine can only move to the next state if there is a clock edge andEnableis true. (It’s an enable on the state register’s updates)

-

Requirements

- You must precisely include and match the names and types/widths of all ports.

- The CEOs of SH Enterprises for some reason still think “Moore is More” and are demanding that a Moore machine be used. (They may not know much about engineering, but they are funding the project so you should follow their request).

- They also ask that you minimize the number of states. There should not be two states with the exact same active outputs.

- As in the prior design, users may want to change between “Regular Wash, Dry, & Sanitize” and “Regular Wash & Power Dry” while the machine is in the first or second cycle of the “Regular Wash” options. You can assume that they will select one of the two and not another mode. (This will probably work naturally if you follow the suggested workflow below)

- SH prizes well-thought-out and clear designs. Part of the grade will be based on having an HDL model that’s easy to read and modify.

- Part of the grade will be based on correct behavior of the machine (unit tests).

- Part of the grade will be based on a hardware demo of the machine.

- The machine should start in an idle state, where it is waiting for

Start. - The machine should return to the idle state when done.

Codespace Tasks

As usual, a variety of tasks are provided in a Codespace to help with your work:

-

1.0 Edit washer.sv: To edit the source for your washer. -

1.1 Simulate washer.sv: To do a live simulation. (Requires manually applying resets, mode, and clock) -

1.2 washer testbench verification: To run the provided testbench -

1.3 Edit washer_tb_in.txt: To view the testbench cases (the original, provided test cases will be used on Gradescope) -

1.4 Edit washer_tb.sv: To view the testbench implementation. -

1.5 washer iCE40 bitstream: Synthesize the HDL model for the iCE 40. -

2.0 Complete questions.md: Open the editor to fill in your responses. -

FPGA Image Server: Run the server that can allow you to program the UPduino. (Only works with Chrome and Edge browsers!)

Validation

SH has provided a testbench to validate that your design matches their expectations. It relies on using signals with matching names and the described behaviors. Test cases are contained in a file named washer_tb_in.txt. Prior to each test case the state machine will be reset. Each test case is a sequence of steps and each step includes: 1) the input values applied and 2) the expected outputs after the clock cycle.

For example, one test case looks like:

9 Mode_0_repeated_cycles

0 1 0 1 0 0 0 0 0 0 0 0 0

0 1 1 0 1 1 0 0 0 0 0 0 0

0 1 1 0 0 1 1 0 0 0 0 0 0

0 1 1 0 0 0 0 0 1 0 0 0 0

0 1 1 0 0 0 0 0 0 0 1 1 0

0 1 1 1 0 0 0 0 0 0 0 0 0

0 1 1 0 1 1 0 0 0 0 0 0 0

0 1 1 0 0 1 1 0 0 0 0 0 0

0 1 1 0 0 0 0 0 1 0 0 0 0

The 9 indicates that there are 9 clock cycles. The Mode_0_repeated_cycles is a rough description of what will be done in this test. Here it indicates that the washer will do repeated cycles of Mode 0 (Regular Wash, Dry, & Extra Sanitize).

Each row consistes of the three inputs used in that clock cycle and the expected outputs. The format is:

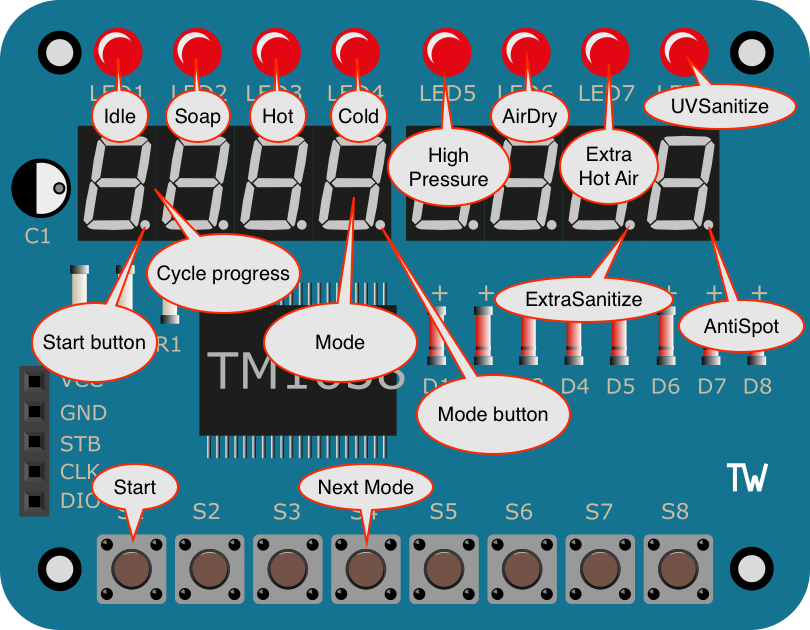

Mode Enable Start Idle Soap Hot Cold HighPressure AirDry ExtraHotAir UVSanitize ExtraSanitize AntiSpot

At the start of this test (2nd line of test: 0 1 0 1 0 0 0 0 0 0 0 0 0) the 4th bit is a 1, indicating that the washer’s Idle output is 1. Notice that columns 2 (Enable) and 3 (Start) are mostly ones because the test is continually advancing to the next state and testing multiple back-to-back wash cycles in Mode 0.

As was the case in prior assignments, part of the grade will be based on submitting code to Gradescope and passing the testbench.

Debugging Tips

Tasks are provided that can allow you to see the contents of the test bench (not strictly required) and the test cases. Here’re some tips that may aid debugging:

Hardware & Demo

Caution!

Please review/complete the FPGA Programming Guide before proceeding! It’s important that:

- A supported browser is used;

- macOS users may need to give permission to connect to the UPduino; and

- Windows users will need to associate a different driver with the UPduino.

This assignment also requires an in-person demo of your final work. Our I/O board will be configured to control the value of the mode, emulate the start button, and display the outputs from your state machine:

Caution!

Double check wiring before proceeding! Errors may cause irreparable damage to the UPduino or LED & Key board! Connections for the UPduino and LED&Key board are included in Studio 4B.

Inputs and Outputs

Overview and Demo

End of work

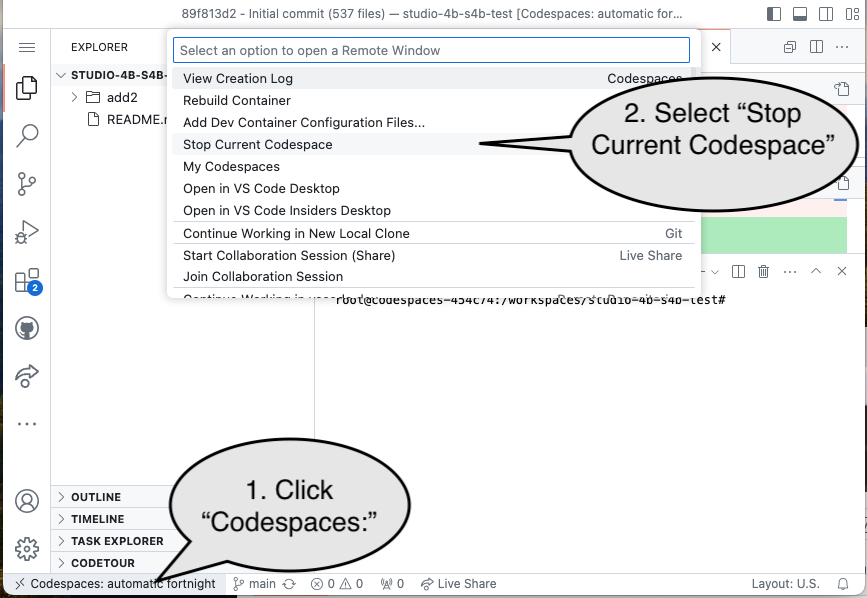

Caution!

Be sure to “stop” your Codespace. You have approximately 60 hours of Codespace time per month. Codespaces often run for ~15 minutes extra if tabs are just closed.

Submission

- Submit work (finished

washer.svandquestions.md) to Gradescope following the process described in Homework 4A. - Stop in during office hours within 10 days (after) the due date to do a live demo/discussion of your work.

- Submission Link: Gradescope